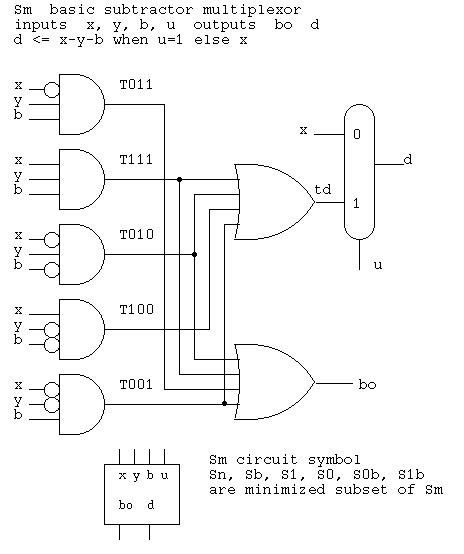

The data in each flip-flop will be shifted to the flip-flop on its right when the rising edge of the clock pulse occurs. Whatever the state of the data input when the rising edge of the clock pulse occurs will be the logic level that is shifted into the first flip-flop. This data can be either a 0 or a 1 and will be shifted to the right on each rising edge of the clock pulse. Data is fed into the D input of the first flip-flop on the left. This shift register is configured to shift data from the left to the right. This is a four bit shift register and therefore consists of four D flip-flops. Shift registers consist of D flip-flops as shown in the figure below. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift Register Operation A register stores data i.e. Two different ways to code a shift register in VHDL are shown. Shift_reg(3) 3) shift_reg(1) shift register bits to the LEDs LED.Ī shift register is written in VHDL and implemented on a Xilinx CPLD. The image below shows an eight bit shift register that is created in VHDL code in this tutorial. Serial Adder Moore FSM: Control Circuit for Automatic Door. Down Counter w/ Toggle FF Up/Down Counter w/ Toggle FlipFlop Set Reset Parallel Shift Register.

JK Shift Register S/R 6-Bit Shift Register 4-Bit Parallel Access Shift Register 4-Bit Universal Shift Register Up Counter w/ Toggle FF.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed